SPERRY RAND

9200/9300

SERIES

PROCESSOR AND STORAGE

PROGRAMMER REFERENCE

| ·                                                                                                                                                                                                                                                               |          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

| This document contains the latest information available at the time of publication. However, the Univ Division reserves the right to modify or revise its contents. To ensure that you have the most receinformation, contact your local Univac Representative. | ac<br>nt |

| UNIVAC is a registered trademark of the Sperry Rand Corporation.                                                                                                                                                                                                |          |

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                                                 |          |

PSS-1

## **PAGE STATUS SUMMARY**

ISSUE: UP-7546 Rev. 1

| Cover/Disclaimer       1         PSS       1         1       1 thru 5         1       1 thru 17         2       1 thru 34         3       1 thru 21         Appendix A       1 thru 3         Appendix B       1 thru 4         Appendix D       1         Index       1 thru 11 | Section          | Page<br>Number | Update<br>Level |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|-----------------|

| Contents 1 thru 5  1 1 thru 17  2 1 thru 34  3 1 thru 21  Appendix A 1 thru 3  Appendix B 1 thru 3  Appendix C 1 thru 4  Appendix D 1                                                                                                                                            | Cover/Disclaimer |                |                 |

| 1 1 thru 17 2 1 thru 34 3 1 thru 21 Appendix A 1 thru 3 Appendix B 1 thru 3 Appendix C 1 thru 4 Appendix D 1                                                                                                                                                                     | PSS              | 1              |                 |

| 2 1 thru 34 3 1 thru 21 Appendix A 1 thru 3 Appendix B 1 thru 3 Appendix C 1 thru 4 Appendix D 1                                                                                                                                                                                 | Contents         | 1 thru 5       |                 |

| 3 1 thru 21  Appendix A 1 thru 3  Appendix B 1 thru 3  Appendix C 1 thru 4  Appendix D 1                                                                                                                                                                                         | 1                | 1 thru 17      |                 |

| Appendix A 1 thru 3  Appendix B 1 thru 3  Appendix C 1 thru 4  Appendix D 1                                                                                                                                                                                                      | 2                | 1 thru 34      |                 |

| Appendix B 1 thru 3  Appendix C 1 thru 4  Appendix D 1                                                                                                                                                                                                                           | 3                | 1 thru 21      |                 |

| Appendix C 1 thru 4 Appendix D 1                                                                                                                                                                                                                                                 | Appendix A       | 1 thru 3       |                 |

| Appendix D 1                                                                                                                                                                                                                                                                     | Appendix B       | 1 thru 3       |                 |

|                                                                                                                                                                                                                                                                                  | Appendix C       | 1 thru 4       |                 |

| Index 1 thru 11                                                                                                                                                                                                                                                                  | Appendix D       | 1              |                 |

|                                                                                                                                                                                                                                                                                  | Index            | 1 thru 11      |                 |

|                                                                                                                                                                                                                                                                                  |                  |                |                 |

| Section | Page<br>Number | Update<br>Level |

|---------|----------------|-----------------|

|         |                |                 |

|         | ,              |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

| Section | Page<br>Number | Update<br>Level |

|---------|----------------|-----------------|

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

|         |                |                 |

## CONTENTS

## PAGE STATUS SUMMARY

## CONTENTS

| 10 111 | 1110 | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | CTION | ۰ |

|--------|------|-----------------------------------------|-------|---|

|        |      |                                         |       |   |

| 1.1. GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-1                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 1.2. SYSTEM CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-4                                                                  |

| 1.3. COMPONENT DESCRIPTION 1.3.1. Processor 1.3.1.1. Main Storage 1.3.1.2. Control 1.3.1.3. Arithmetic 1.3.1.3.1. Multiply, Divide, and Edit 1.3.1.3.2. Subtraction by Two's Complement Method 1.3.1.4. Input/Output 1.3.1.4.1. Multiplexer Channel 1.3.1.4.2. Selector Channel 1.3.2. Printer 1.3.2.1. 300 LPM Print Speed 1.3.2.2. 120 Print Positions 1.3.2.3. Print Position Expansion 1.3.2.4. 132 Print Positions 1.3.2.5. Variable Speed Printing 1.3.2.6. 8 LPI Print Spacing | 1-9 1-9 1-9 1-9 1-9 1-9 1-10 1-11 1-11 1                             |

| 1.3.2.7. Form Alignment 1.3.2.8. High Speed Numeric Print                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-13<br>1-13                                                         |

| 1.4. DATA FORMATS AND CODES 1.4.1. Binary Number Representation 1.4.2. Hexadecimal Representation 1.4.3. Decimal Number Representation 1.4.3.1. Sign Bits 1.4.4. Character Representation 1.4.5. Parity Verification 1.4.6. OP Codes 1.4.7. Logical Information                                                                                                                                                                                                                       | 1-13<br>1-14<br>1-15<br>1-15<br>1-16<br>1-16<br>1-17<br>1-17<br>1-17 |

| 1.4.7. Logical infolliation                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-1/                                                                 |

## 2. PROCESSOR UNIT

| <ul> <li>2.1. MAIN STORAGE</li> <li>2.1.1. Privileged and Low Order Storage</li> <li>2.1.2. Storage Boundaries</li> <li>2.1.3. Parity Checking</li> <li>2.1.4. Interrupts</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-1<br>2-1<br>2-2<br>2-3<br>2-3                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

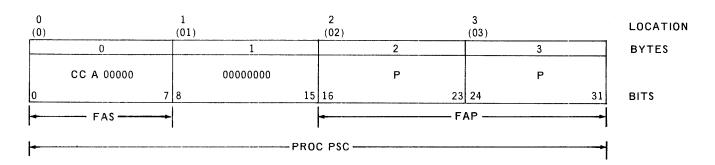

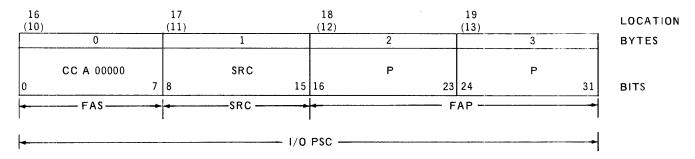

| 2.2. PROCESSOR CONTROL 2.2.1. Program State Control 2.2.1.1. Processor Program State Control Words (Bytes 0-3) 2.2.1.2. Input/Output Program State Control Word (Bytes 16-19) 2.2.2. Restricted Alter/Display and Operator Request (Bytes 4, 5) 2.2.3. Machine Instruction Register (Bytes 6-11) 2.2.4. Restart Instruction Register (Bytes 22-25) 2.2.5. Special Status (Bytes 29-31) 2.2.6. Processor Program Register (Bytes 32-47) and Input/Output Program Registers (Bytes 48-63) 2.2.7. Device Status (Byte 66) and Device Address (Byte 67) 2.2.8. Buffer Control Words (Bytes 68-127) 2.2.8.1. Multiplexer Subchannel BCW 2.2.8.2. Device Control Subchannel Numbering 2.2.8.3. Buffer Control Word Location 2.2.8.4. Additional Nonshared Subchannel Device Addresses 2.2.9. Printer Image Area (Bytes 128-259) 2.2.10. Printer Control 2.2.10.1. Printer Instructions 2.2.10.2. Printer Buffer Control Word 2.2.10.3. Issue and Execute 2.2.10.4. Status Register 2.2.10.5. Interrupt Requests 2.2.10.6. Printer Status Byte 2.2.11. Input/Output Control 2.2.12. Operator-Initiated Functions 2.2.12.1. Load Cycle 2.2.12.2. Alternate Execute and Staticize Cycle | 2-4<br>2-6<br>2-6<br>2-7<br>2-7<br>2-7<br>2-8<br>2-8<br>2-8<br>2-9<br>2-9<br>2-9<br>2-10<br>2-10<br>2-10<br>2-10<br>2-11<br>2-12<br>2-12<br>2-13<br>2-14<br>2-15<br>2-15 |

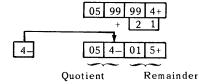

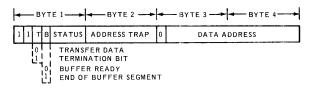

| 2.3. MULTIPLEXER CHANNEL CONTROL 2.3.1. Multiplexer Channel Instructions 2.3.2. Multiplexer Channel Buffer Control Word 2.3.3. Multiplexer Channel Status Byte 2.3.4. Condition Code 2.3.5. Alternate BCW Format 2.3.5.1. Data Direction Control 2.3.6. Polling 2.3.6.1. Priority of Interrupt 2.3.7. Special Channel Instructions and Interrupts 2.3.7.1. Operator Interrupt 2.3.7.2. Alternate (LT) Summary Interrupt 2.3.7.3. One-Second Interrupt 2.3.7.4. Summary of Special Channel Instructions 2.3.8. Channel Checking 2.3.8.1. Interface Error Flip-Flop 2.3.8.2. Device Address Parity 2.3.8.3. Parity Error Flip-Flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-15<br>2-16<br>2-17<br>2-17<br>2-17<br>2-18<br>2-19<br>2-20<br>2-20<br>2-20<br>2-21<br>2-21<br>2-21<br>2-22<br>2-22<br>2-22<br>2-22                                     |

| UP-7546<br>Rev. 1 | UNIVAC 9200/9200 II/9300/9300 II<br>PROCESSOR AND STORAGE | Contents | 3<br>Page: |

|-------------------|-----------------------------------------------------------|----------|------------|

|                   |                                                           |          |            |

|    | 2.4.1. Channel Addressing 2.4.1.1. Selector Channel Address Format 2.4.1.2. Multiplexer Channel Address Format 2.4.2. Processor Lock-Out 2.4.3. Concurrent Operations 2.4.4. Command Chaining 2.4.5. Execute I/O and Test I/O Instructions 2.4.6. I/O Commands 2.4.7. Transfer-in-Channel (TIC) Command 2.4.8. Condition Code (CC) 2.4.9. Channel Address Word (CAW) and Diagnostic Interrupt 2.4.10. Channel Command Word (CCW) 2.4.11. Device Status 2.4.12. Channel Status Word (CSW) 2.4.13. Channel Checking 2.4.14. Special Selector Channel Instructions                                                                                                                                                                                                                                                 | 2-23<br>2-23<br>2-23<br>2-23<br>2-24<br>2-24<br>2-25<br>2-25<br>2-26<br>2-26<br>2-27<br>2-28<br>2-30<br>2-30<br>2-31    |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

|    | 2.5. DATA TRANSLATION 2.5.1. Card Code Translation (80-Column Card) 2.5.1.1. Card Code Image Mode (80-Column Card) 2.5.2. Card Code Translation (90-Column Card) 2.5.2.1. Card Code Image Mode (90-Column Card) 2.5.3. Internal Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-31<br>2-31<br>2-32<br>2-33<br>2-34<br>2-34                                                                            |

| 3. | INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                         |

|    | 3.1. GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-1                                                                                                                     |

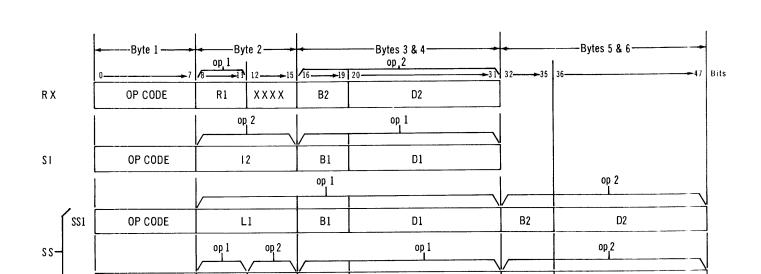

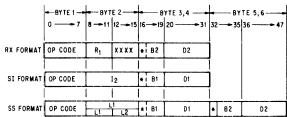

|    | 3.2. INSTRUCTION FORMAT 3.2.1. Register and Indexed Storage Operation (RX) 3.2.2. Storage and Immediate Operand Operation (SI) 3.2.3. Storage-to-Storage (SS1) 3.2.4. Storage-to-Storage (SS2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-6<br>3-6<br>3-6<br>3-7                                                                                                |

|    | 3.3. INSTRUCTION REPERTOIRE 3.3.1. Binary Instructions and Overflow 3.3.1.1. Store Halfword Instruction (STH) 3.3.1.2. Load Halfword Instruction (LH) 3.3.1.3. Compare Halfword Instruction (CH) 3.3.1.4. Add Immediate Instruction (AI) 3.3.1.5. Add Halfword Instruction (AH) 3.3.1.6. Subtract Halfword Instruction (SH) 3.3.2. Logical Instructions 3.3.2.1. Test Under Mask Instruction (TM) 3.3.2.2. Move Immediate Instructions (MVI) 3.3.2.3. AND Immediate Instruction (NI) 3.3.2.4. Compare Logical Immediate Instruction (CLI) 3.3.2.5. OR Immediate Instruction (HPR) 3.3.2.6. Halt and Proceed Instruction (MVN) 3.3.2.8. Move Character Instruction (MVC) 3.3.2.9. AND Character Instruction (NCC) 3.3.2.10. Compare Logical Character Instruction (CLC) 3.3.2.11. OR Character Instruction (OCC) | 3-7<br>3-8<br>3-9<br>3-9<br>3-9<br>3-10<br>3-10<br>3-10<br>3-10<br>3-11<br>3-11<br>3-11<br>3-11<br>3-11<br>3-11<br>3-11 |

|    | 3.3.2.11. UK Unaracter instruction (UU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-17                                                                                                                    |

| UP-7546<br>Rev. 1 | UNIVAC 9200/9200 II/9300/9300 II<br>PROCESSOR AND STORAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        | Contents                                                                                                             | PAGE |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------|------|

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |                                                                                                                      |      |

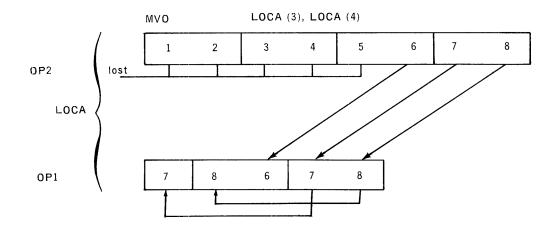

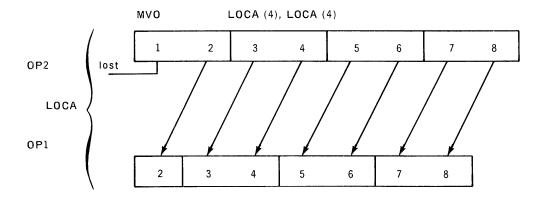

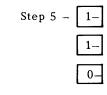

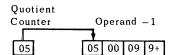

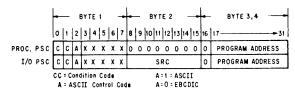

|                   | 3.3.2.12. Translate Instruction (TR) 3.3.2.13. Edit Instruction (ED) 3.3.3. Decimal Instructions 3.3.3.1. Move with Offset Instruction (MVO) 3.3.3.2. Pack Instruction (PACK) 3.3.3.3. Unpack Instruction (UNPK) 3.3.3.4. Zero Add (Packed) Decimal Instruction (ZAP) 3.3.3.5. Compare (Packed) Decimal Instruction (CP) 3.3.3.6. ADD (Packed) Decimal Instruction (AP) 3.3.3.7. Subtract (Packed) Decimal Instruction (SP) 3.3.3.8. Multiply (Packed) Decimal Instruction (MP) 3.3.3.9. Divide (Packed) Decimal Instruction (DP) 3.3.4. Branch Instructions 3.3.4.1. Branch-on-Condition Instruction (BC) 3.3.4.2. Branch and Link Instruction (BAL) 3.3.5. State Control (Privileged and Special) Instructions 3.3.5.1. Load Program State Control Instruction (LPSC) |        | 3-12<br>3-13<br>3-13<br>3-14<br>3-15<br>3-15<br>3-15<br>3-16<br>3-16<br>3-18<br>3-20<br>3-20<br>3-20<br>3-20<br>3-20 |      |

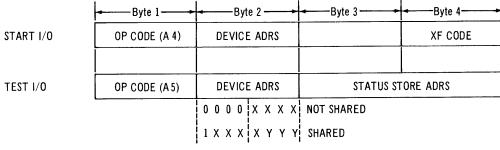

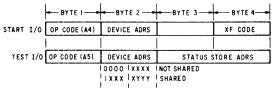

|                   | <ul> <li>3.3.5.2. Store Program State Control Instruction (SPSC)</li> <li>3.3.5.3. Supervisor Request Call Instruction (SRC)</li> <li>3.3.6. Input/Output Instruction</li> <li>3.3.6.1. Execute I/O Instruction (XIOF)</li> <li>3.3.6.2. Test I/O Instruction (TIO)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        | 3-21<br>3-21<br>3-21<br>3-21<br>3-21                                                                                 | :    |

|                   | APPENDIXES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |                                                                                                                      |      |

|                   | A. INSTRUCTIONS, FORMATS, CODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |                                                                                                                      |      |

| I                 | B. HEXADECIMAL TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |                                                                                                                      |      |

|                   | C. CHARACTER GRAPHIC SET CODES AND PRINTER SYNCHRONIZER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R CODE |                                                                                                                      |      |

|                   | D. POWERS OF 2; POWERS OF 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |                                                                                                                      |      |

|                   | INDEX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |                                                                                                                      |      |

|                   | TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |                                                                                                                      |      |

|                   | 1-1. Configurations for UNIVAC 9200 and 9300 Systems Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | 1-4                                                                                                                  |      |

|                   | 1-2. Hexadecimal-Decimal Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        | 1-15                                                                                                                 |      |

|                   | 3-1. Instruction Mnemonics in Alphabetical Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        | 3-2                                                                                                                  |      |

|                   | 3-2. Instructions Grouped by Functional Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        | 3-3                                                                                                                  |      |

|                   | 3-3. Instructions Grouped by Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        | 3-4                                                                                                                  |      |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |                                                                                                                      |      |

3-4. Instructions in Sequence of Hexadecimal Codes

3-5

Contents

PAGE:

5

**FIGURES**

| 1-1. | UNIVAC 9200/9200 II/9300/9300 II Systems Processor               | 1-1  |

|------|------------------------------------------------------------------|------|

| 1-2. | UNIVAC 9200/9200 II/9300/9300 II Systems Processor Block Diagram | 1-2  |

| 1-3. | Configuration for UNIVAC 9200 System Processor                   | 1-5  |

| 1-4. | Configuration for UNIVAC 9200 II System Processor                | 1-6  |

| 1-5. | Configuration for UNIVAC 9300 System Processor                   | 1-7  |

| 1-6. | Configuration for UNIVAC 9300 II System Processor                | 1-8  |

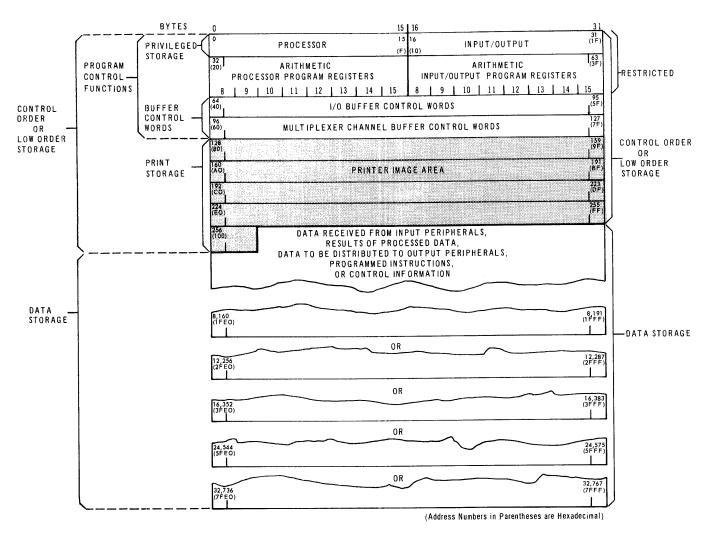

| 2-1. | Main Storage Organization                                        | 2-2  |

| 2-2. | Organization of First 260 Bytes of Storage                       | 2-5  |

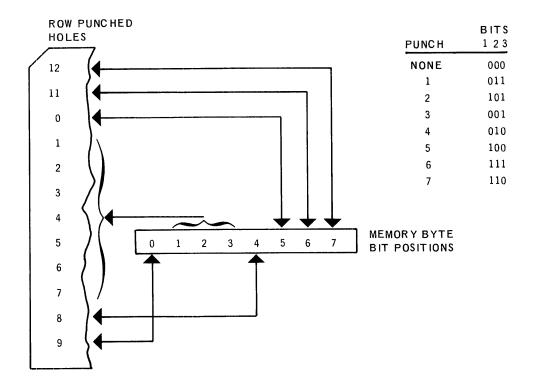

| 2-3. | Compressed Code for 80-Column Card                               | 2-32 |

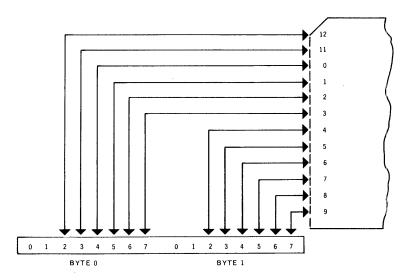

| 2-4. | Image Mode for 80-Column Card                                    | 2-33 |

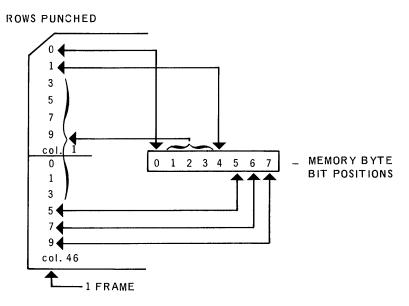

| 2-5. | Card Code Translation for 90-Column Card                         | 2-33 |

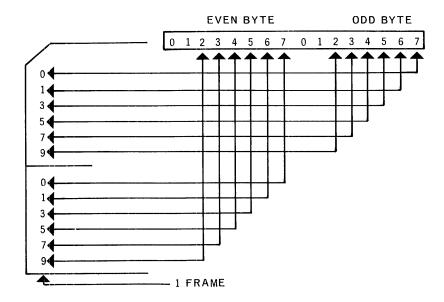

| 2-6. | Image Mode for 90-Column Card                                    | 2-34 |

| 3-1. | Instruction Formats                                              | 3-7  |

# 1. INTRODUCTION

Figure 1-1. UNIVAC 9200/9200 II/9300/9300 II Systems Processor

## 1.1. GENERAL

This document contains a description of the UNIVAC 9200/9200 II/9300/9300 II Systems processor with optional features pertaining to expansion, internal operation of the processor, data and program information presentation, instruction repertoire and coding, and constant and storage definitions.

It should be noted that only one processor is detailed herein with the specific differences between each noted as required. The four system processors are identical in appearance. The configuration is shown in Figure 1-1.

This manual is divided into the following basic sections:

- Introduction

- Processor Unit

- Instructions

- Appendix

The appendix contains tables, charts, and diagrams as a convenience to the programmer and field engineer. The fact that many examples and explanations are given in terms of punched card input does not imply that any other of the usual input methods may not be used.

The UNIVAC 9200/9200 II/9300/9300 II Systems processor shown in Figure 1-1, is a byte-oriented data processor integrated with an attached printer and an optional externally-connected card punch and card reader (basic peripherals). A wide range of other peripheral devices may be incorporated either initially by replacing one or more of these basic peripheral devices, or later, by adding to the system.

Two major functions of the processor are decoding and storage. The decoding function analyzes each instruction to determine required operations and the location of needed information. An instruction containing labels of data in storage is decoded to find the addresses and lengths of the operands (data to be processed), as well as the particular operation that is to be performed on the data. The processor then responds to the instruction by using generated control signals. The storage (memory) portion of the processor stores the data and instructions required by the program in addressable locations that are easily accessible to the program.

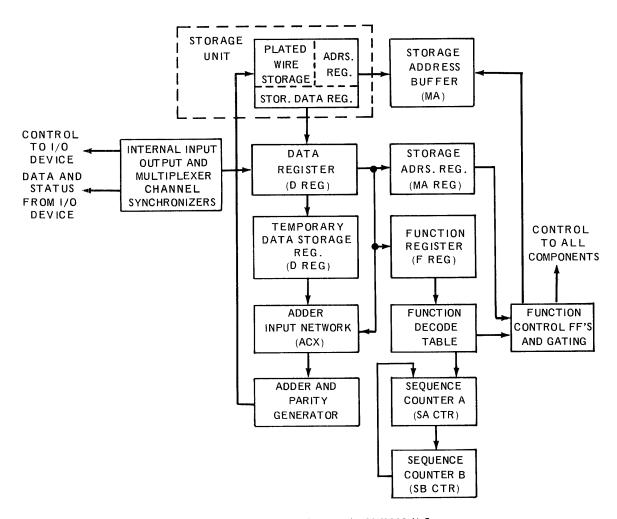

The major components of the UNIVAC 9200/9200 II/9300/9300 II Systems processor are shown in Figure 1-2.

Figure 1-2. UNIVAC 9200/9200 II/9300/9300 II Systems

Processor Block Diagram

SECTION: PAGE:

They are controlled and coordinated by means of internally stored programs which are derived from a standard instruction repertoire. The function of each of the components is as follows:

- Storage Unit Comprises registers used in the processing and storage of all instructions and data that is to be, or has been, processed.

- Data Register Provides temporary storage for data that is currently being (D Reg) processed. All transfer of data between the processor or peripheral units and the storage unit is accomplished through the data register.

- Temporary Provides additional temporary storage for data currently being processed, and also for various special codes required for process control and addressing.

(B Reg)

- Adder Input Gates, modifies, and generates data involved in processing Network program data or special control codes.

(ACX)

- Adder and Parity

Generator

Performs various processes specified by the instructions, such as addition, subtraction, and the formation of AND- and OR- products. Also generates parity.

- Storage (Memory) Addresses of data being processed. Address Buffer (MA)

- Storage (Memory) Stores the addresses of data currently being processed.

Address Register

(MA Reg)

- Function Register Stores the partial decoded function code specified in an (F Reg) instruction.

- Function Decode Interprets instructions and generates the control signals

Table required for the initiation of the required process.

- Sequence Counters

A and B outputs of both counters control the generating of function signals, sequence counter A is used as a first-stage input to the second-stage sequence counter B.

- Function Control Contains all of the secondary storage and gating circuitry Flip-flops and Gating for generation of the control signals necessary to initiate the various subfunctions of a specified process.

PAGE:

1.2. SYSTEM CONFIGURATION

The UNIVAC 9200/9200 II/9300/9300 II Systems processor is housed in two separate cabinets. The larger of the two cabinets contains an operator's control panel, a printer, and the integrated logic circuit packages. The second cabinet is the electronics cabinet; it contains the storage (memory) circuitry and the power supplies and power distribution panel for the entire processor.

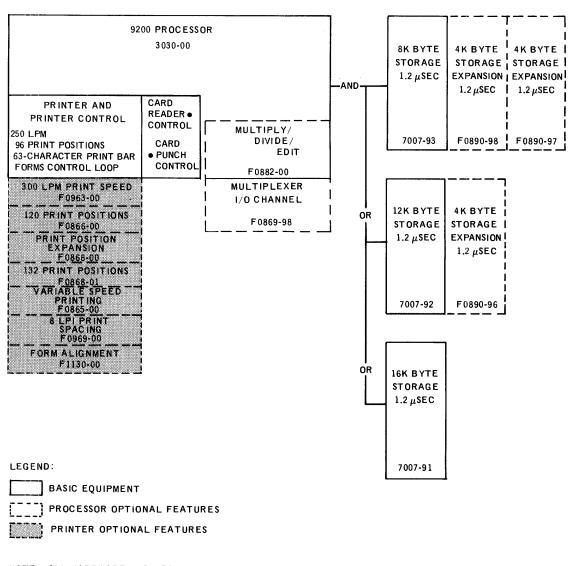

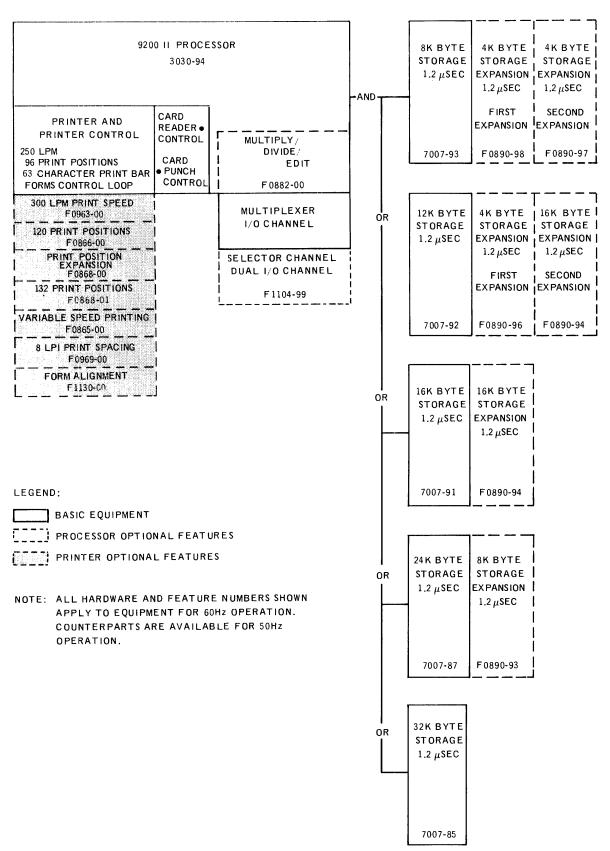

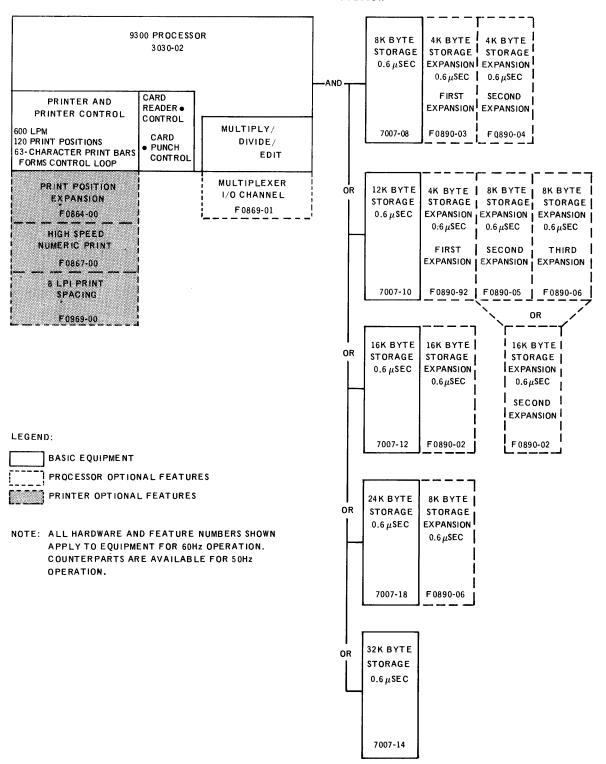

Table 1-1 lists the basic and optional processor equipment for each of the four systems (UNIVAC 9200, 9200 II, 9300, 9300 II). Figures 1-3, 1-4, 1-5, and 1-6 illustrate the system configurations for these systems.

| UNIVAC SYSTEMS PROCESSORS                                                                                      |                                                                                                                       |                                                                                                                                             |                                                                                                                       |  |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

| 9200                                                                                                           | 9200 11                                                                                                               | 9300                                                                                                                                        | 9300 11                                                                                                               |  |

| Printer Processor                                                                                              | Printer Processor                                                                                                     | Printer Processor                                                                                                                           | Printer Processor                                                                                                     |  |

| o Control<br>o Printer                                                                                         | o Control<br>o Printer                                                                                                | o Control<br>o Printer                                                                                                                      | o Control<br>o Printer                                                                                                |  |

| o Form control loop<br>o 250 LPM bar printer<br>96 print positions                                             | o Form control loop<br>o 250 LPM bar printer<br>96 print positions                                                    | o Form control loop<br>o 600 LPM bar printer<br>120 print positions                                                                         | o Form control loop<br>o 600 LPM bar printer<br>120 print positions                                                   |  |

| 63 character print bar o 8K-byte storage Expandable to 16K bytes 1.2 µsec. cycle time                          | 63 character print bar o 8K-byte storage Expandable to 32K bytes 1.2 \( \alpha \) sec. cycle time                     | 63 character print bar  o 8K-byte storage  Expandable to 32K bytes  0.6 µsec. cycle time                                                    | 63 character print bar o 16K-byte storage Expandable to 32K bytes 0.6 µsec. cycle time                                |  |

| o Arithmetic Control<br>Control for printer,<br>punch, and reader                                              | o Arithmetic Control<br>Control for printer,<br>punch, and reader                                                     | o Arithmetic Control<br>Control for printer,<br>punch, and reader                                                                           | o Arithmetic/Control<br>Control for printer,<br>punch, and reader                                                     |  |

| * Multiplexer channel;<br>accesses up to 8 sub-<br>systems or another<br>processor<br>* Multiply, divide, edit | o Multiplexer channel; accesses up to 8 sub- systems or another processor * Multiply, divide, edit * Selector channel | <ul> <li>Multiplexer channel;</li> <li>accesses up to 8 subsystems or another</li> <li>processor</li> <li>Multiply, divide, edit</li> </ul> | o Multiplexer channel; accesses up to 8 sub- systems or another processor o Multiply, divide, edit o Selector channel |  |

| † 300 LPM print speed                                                                                          | † 300 LPM print speed                                                                                                 |                                                                                                                                             |                                                                                                                       |  |

| <ul> <li>† 120 print positions</li> <li>† Print position expansion</li> <li>† 132 print positions</li> </ul>   | † 120 print positions † Print position expansion † 132 print positions                                                | † Print position expansion                                                                                                                  | † Print position expansion                                                                                            |  |

| <ul> <li>Variable speed printing</li> <li>8 LPI print spacing</li> <li>Form alignment</li> </ul>               | † Variable speed printing † 8LP1 print spacing † Form alignment                                                       | † High speed numeric print<br>† 8 LPI print spacing                                                                                         | † High speed numeric print<br>† 8 LPI print spacing                                                                   |  |

#### LEGEND:

- o Basic Equipment

- \* Processor Optional Features

- † Printer Optional Features

Table 1—1. Configurations for UNIVAC 9200 and 9300 Systems Processors

SECTION: PAGE:

#### UNIVAC 9200 SYSTEM PROCESSOR

NOTE: ALL HARDWARE AND FEATURE NUMBERS SHOWN APPLY TO EQUIPMENT FOR 60Hz OPERATION.

COUNTERPARTS ARE AVAILABLE FOR 50Hz OPERATION.

Figure 1-3. Configuration for UNIVAC 9200 System Processor

1

SECTION: PAGE:

#### UNIVAC 9200 II SYSTEM PROCESSOR

Figure 1-4. Configuration for UNIVAC 9200 II System Processor

#### UNIVAC 9300 SYSTEM PROCESSOR

Figure 1-5. Configuration for UNIVAC 9300 System Processor

8

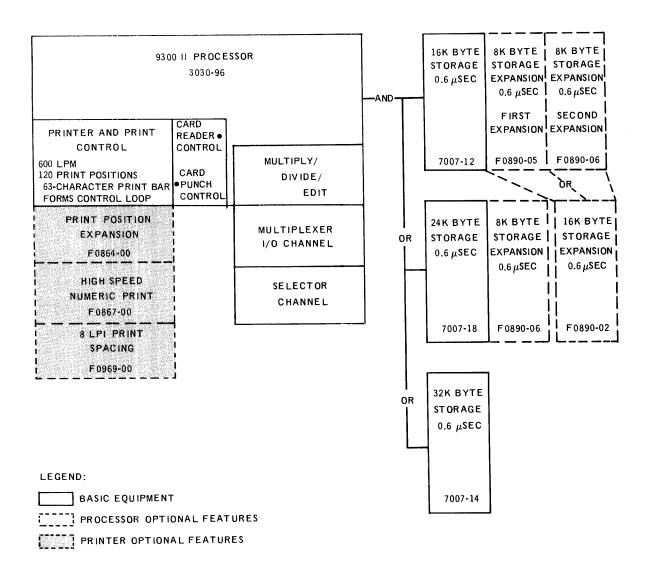

## UNIVAC 9300 II SYSTEM PROCESSOR

NOTE: ALL HARDWARE AND FEATURE NUMBERS SHOWN APPLY TO EQUIPMENT FOR 60Hz OPERATION.

COUNTERPARTS ARE AVAILABLE FOR 50Hz OPERATION.

Figure 1-6. Configuration for UNIVAC 9300 II System Processor

PAGE:

## 1.3. COMPONENT DESCRIPTION

Components for the different systems are generally rather similar. For this reason, the descriptions which follow apply, with exceptions noted, regardless of the system in which the component is used.

#### 1.3.1. Processor

The major portions of the UNIVAC 9200/9200 II/9300/9300 II Systems processor are the main storage, control, arithmetic, and input and output.

## 1.3.1.1. Main Storage

The main storage portions of the processor is a separate free standing unit connected to the printer processor cabinet. The storage elements are of the plated wire, cylindrical thin film type. The storage unit operates either in a read, write, or lockout mode at a cycle rate of 1.2 microseconds for the UNIVAC 9200 and 9200 II Systems processor; and at a rate of 0.6 microseconds for the UNIVAC 9300 and 9300 II Systems processor. Reading is nondestructive; that is, the data is not erased from storage by the read process.

The main storage is used to hold data received from input peripherals, results of processing, data to be distributed to output peripherals, programmed instructions, and control information.

The minimum basic storage is 8,192 bytes of nine bits each (eight data bits and one parity bit), except that the UNIVAC 9300 II Systems processor has a minimum of 16,384 bytes. The basic storage units may be expanded to 12,288, 16,384, 24,576, or 32,768 bytes except for the UNIVAC 9200 Systems processor, which is limited to 16,384 bytes.

## 1.3.1.2. Control

The control portion of the processor controls the sequence, interpretation, and execution of each instruction. The cycling of main storage is initiated by this section. All of the hardware aspects of interrupt handling, error checking, and protection are performed by the control section. The control section maintains the program address location counter and provides for the different processor modes of operation.

#### 1.3.1.3. Arithmetic

The arithmetic portion of the processor performs data manipulations including binary and decimal arithmetic operations, and logical operations. The basic UNIVAC 9200 and 9200 II Systems processor is limited to machine addition only. Subtraction is performed by converting the subtrahend to its two's complement and adding. To multiply and divide, a suitable subroutine must be inserted into the user's program. The Multiply, Divide, and Edit capability (see 1.3.1.3.1) is available as an option.

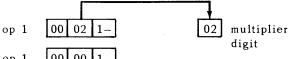

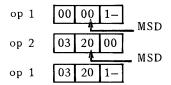

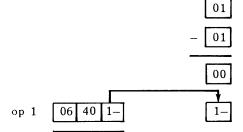

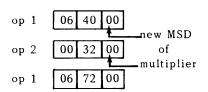

## 1.3.1.3.1. Multiply, Divide, and Edit

The UNIVAC 9300 and 9300 II Systems processor has a multiply/divide/edit instruction set which includes decimal multiplication and division, and additional editing features. This capability is optional for the UNIVAC 9200 and 9200 II Systems processor.

## 1.3.1.3.2. Subtraction by Two's Complement Method

Because the fundamental arithmetic operation of the processor is addition, to perform subtraction it is necessary to add the two's complement of the subtrahend to the minuend. Let M and S be the absolute values of the minuend and subtrahend respectively. Then:

$$\begin{array}{c} (+M)-(+S) \\ (+M)-(-S) \\ (-M)-(+S) \\ (-M)-(-S) \end{array} \text{ is converted to } \begin{cases} (+M)+(+S)^{1} \\ (+M)+(-S)^{1} \\ (-M)+(+S)^{1} \\ (-M)+(-S)^{1} \end{cases}$$

where ()' denotes the two's complement of the original value.

By definition, the two's complement of a binary number (N) with n digit positions is:

$$2^{n}-N$$

Thus for eight-bit binary number (N), the two's complement is  $2^8-N$  or, in binary notation, 100000000-N.

The two's complement of the binary number 00111001, for example, is:

$$\frac{100000000}{-00111001}$$

$$\frac{11000111}{}$$

Note that actual subtraction is not required, since the two's complement can be obtained by inspection of the number. Each bit of the number is simply inverted, that is, a 1 is changed to a 0, and a 0 is changed to a 1; a 1 is then added to the least significant bit at right. Thus the

which agrees with the result obtained above.

Example:

It is desired to subtract +58 from another number. This is done by adding the two's complement of 58. What is the value?

Binary equivalent 0011 1010

One's complement 1100 0101

+ 1

Two's complement  $\overline{1100\ 0110}$  This is the desired value.

Suppose 58 were to be subtracted from 17, where the representation of 17 is  $0001\ 0001$ .

The addition is represented 0001 0001 1100 0110 1101 0111

The 1 in the most significant bit position indicates a negative value; therefore the two's complement is required. This is  $-(0010\ 1000+1) = -(0010\ 1001)$  which is -41.

## 1.3.1.4. Input/Output

The input/output portion of the processor, through the use of input/output instructions, provides the means of initiating the operation of all peripheral devices associated with the processor and of determining the status of each device. This portion of the processor also directs the transfer of data between main storage and the peripheral system. After control of the input/output function has been transferred to the control unit for a particular device, data transfer is performed concurrently with the processor functions.

## 1.3.1.4.1. Multiplexer Channel

The multiplexer channel (standard with the UNIVAC 9200 II and 9300 II Systems processor and optional with the UNIVAC 9200 and 9300 Systems processor) provides an interface for devices other than the basic peripheral devices, card punch, and card reader. The multiplexer channel accepts I/O instructions from the processor and sends I/O requests to the connected peripheral devices, one at a time. The multiplexer channel places the device address and all signals needed to ascertain the status of the device on the multiplexer channel output line (bus) to the device. The peripheral device responds with a byte of information containing its status. The multiplexer channel decodes this status byte and generates generates a condition code for the processor. If there is no traffic to be executed, or if the device is not at that time ready to handle traffic, the multiplexer channel tests the next peripheral device in a predetermined order; if there is no traffic to be executed, the sequence specified by the processor's program is executed.

The multiplexer channel is asynchronous; it depends on the processor and the control unit of the peripheral device for instructions. The channel generates the necessary sequences to respond to sequences initiated by the control unit, making use of the processor's flip-flop registers and arithmetic circuits on a time-sharing basis. This permits the multiplexer channel to work several peripheral devices in sequence by assigning the multiplexer channel interface to the first peripheral device long enough to transfer one or a few bytes of information. When the processor finishes its operation with the first peripheral device, it operates similarly with the other peripheral devices before returning to the first. The processor must test each peripheral device for availability before an information transfer can take place.

The maximum transfer rate for one control unit in burst mode is 98K bytes per second. To achieve this rate, the control unit must respond with the leading edge of Service In at the input to the channel within 1.3 microseconds following the trailing edge of Service Out at the output of the channel. If the control unit response time is greater than 1.3 microseconds the maximum transfer rate is reduced as follows:

- If greater than 1.3 microseconds but less than 2.45 microseconds, the maximum transfer rate is 87.7K bytes per second.

- If greater than 2.45 microseconds but less than 3.65 microseconds, the maximum transfer rate is 79.5K bytes per second.

PAGE:

The maximum transfer rate for one control unit in multiplex mode is 75.8K bytes per second. To achieve this rate the control unit must respond with the leading edge of Address In at the input to the channel within 350 nanoseconds following the leading edge of Select Out at the output of the channel. This time must include all delays caused by propagation of the Select signal, cable lengths, control unit receivers and drivers, and control unit logic. Ordinarily, this can be achieved only by the highest priority control unit. The typical maximum rate for a control unit, other than the highest priority control unit is 72.5K bytes per second. To maintain these two transfer rates (75.8K and 72.5K bytes per second) the control unit must have the Request In signal active at the channel 1.2 microseconds following the trailing edge of the Service Out signal at the output of the channel.

For a control unit that does not meet the Request In requirements, the maximum transfer rate drops to 57.2K bytes per second. This rate uses the average processor latency time of 8.5 microseconds. Again to achieve this transfer rate of 57.2 bytes per second, the control unit must respond with the leading edge of the Request In signal at the input to the channel within 4.5 microseconds following the trailing edge of Service Out signal at the output of the channel.

The maximum transfer rate, for more than one control unit in multiplex mode when connected in such a configuration as to keep Request In signal active continuously is 72.5K bytes per second. This rate considers the typical response times from the control units, the Select Out propagation time through higher priority control units and the fact that the channel interface bus cable can be connected to eight control units.

#### 1.3.1.4.2. Selector Channel

The selector channel, standard with UNIVAC 9300 II Systems processor and optional with UNIVAC 9200 II System processor, provides additional I/O capability for eight subsystems such as a disc subsystem. Maximum transfer rate of the selector channel is 350K bytes per second, including command chaining when operating in burst mode.

The selector channel operates with a higher priority than the multiplexer channel, thereby permitting the selector channel to gain access to the storage area at any time.

#### 1.3.2. Printer

A bar printer with a 63-character print bar is included in the main cabinet of the processor. For the basic UNIVAC 9200/9200 II equipment, printing speed is 250 lines per minute; there are 96 print positions per line. For the UNIVAC 9300 and 9300 II equipment, printing speed is 600 lines per minute and there are 120 print positions. See Appendix A for additional type bars available for the printer.

Optional features available for the printer are described in the subsections as follows.

#### 1.3.2.1. 300 LPM Print Speed

The 300 LPM print speed feature, optional with the UNIVAC 9200 and 9300 II Systems processor, increases the print speed of the printer from 250 LPM to 300 LPM. When used with variable speed printing feature, the variable speed is increased from 250/500 LPM to 300/600 LPM.

PAGE:

#### 1.3.2.2. 120 Print Positions

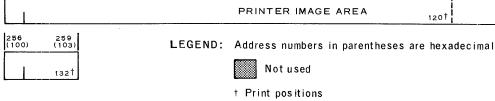

The 120 print position feature, optional with the UNIVAC 9200 and 9200 II Systems processor and standard with the 9300 and 9300 II Systems processor, adds 24 additional print positions to the basic 96, to provide 120 print positions.

## 1.3.2.3. Print Position Expansion

The print position expansion feature, optional with the UNIVAC 9200, 9200 II, 9300, 9300 II Systems processors, permits a 120-position printer to be expanded up to 132 print positions. This option can be added after equipment installation.

## 1.3.2.4. 132 Print Positions

The 132 print position feature, optional only with the UNIVAC 9200 and 9200 II Systems processor, permits a 96-position printer to be expanded up to 132 print positions. This option can be adopted after equipment installation.

#### 1.3.2.5. Variable Speed Printing

Variable speed printing, optional only with UNIVAC 9200 and 9200 II Systems processor, converts the 63 character, 250 LPM printer to a printer capable of printing a 48 character set at 250 LPM, and through program control automatically switches to 500 LPM if the line to be printed contains only characters of the 16 character numeric set. This allows automatic switching between 250 LPM and 500 LPM depending on characters to be printed on a line. After installation of the feature, 63 character and 48/16 character bars are interchangeable.

## 1.3.2.6. 8 LPI Print Spacing

Print spacing at eight line per inch, optional with UNIVAC 9200, 9200 II, 9300, 9300 II Systems processor, permits the operator to select vertical print spacing of either 6 or 8 lines per inch.

## 1.3.2.7. Form Alignment

Form alignment, optional with UNIVAC 9200 and 9200 II Systems printers, provides vernier tractors and a single turn phasing knob, which are standard with the UNIVAC 9300 and 9300 II Systems processor printers.

## 1.3.2.8. High Speed Numeric Print

High speed numeric print, optional only with the UNIVAC 9300 and 9300 II Systems processor, permits conversion of the 63 character 600 LPM printer portion of the processor to a 16 character, 1200 LPM numeric set. After installation of the feature, 63 character and 16 character bars are interchangeable.

SECTION:

## 1.4. DATA FORMATS AND CODES

The data formats used in storage are as follows:

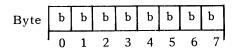

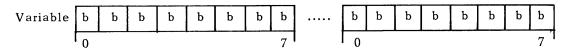

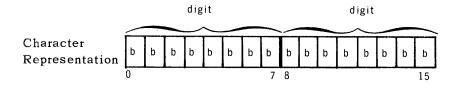

One byte consists of eight data bits numbered 0 to 7, left to right, as shown:

where b denotes a bit.

Halfword data format consist of two consecutive bytes, starting at an even address such as 0, 2, 4, the binary representation being within 16 bits and having the leftmost bit as the sign (S) bit of the data:

It is possible to store 256 different bit combinations in 2 bytes.

Fullword data formats consist of four consecutive bytes if the most significant byte address is divisible by four.

Instructions use 4 to 6 bytes and are restricted to the halfword boundary.

Variable data formats have a variable number of consecutive bytes:

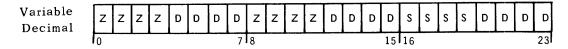

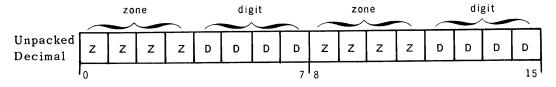

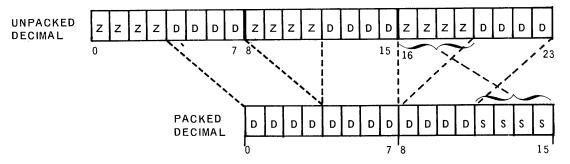

The data format of unpacked decimal representation is variable in length. A three digit decimal number, for example, is stored in three bytes as shown in the sketch, where ZZZZ = zone, DDDD = digit, SSSS = sign.

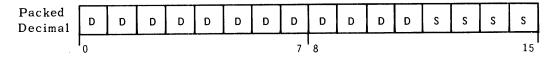

Packed decimal representation is also variable in length, A three digit decimal number is stored in a two byte packed decimal field when DDDD = digit, SSSS = sign.

A C E .

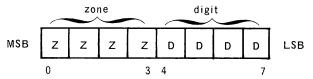

Data can be represented in various forms by the programmer; but certain restrictions are imposed if the data is to be printed or processed arithmetically. The contents of a byte can be considered as a binary number, a decimal number, or two packed decimal numbers, an alphabetic or symbolic character, or logical information. A field used to represent a binary number uses all of the bit positions (except the sign bit) to contain the value. However, each byte in a field representing a decimal number, alphabetic character, or symbol is considered to be divided into zone and digit portions. The zone portion is the most significant four bits; the digit portion is the least significant four bits.

## 1.4.1. Binary Number Representation

Binary numbers in the registers make use of the most significant bit (MSB) as the sign indicator. A 0 in the most significant position indicates a positive number and a 1 indicates a negative number. It should be noted that since the MSB is the sign bit, a binary value of only  $\pm 32 \, \mathrm{K}$  may be expressed. Negative numbers are expressed by the two's complement value of the number.

#### 1.4.2. Hexadecimal Representation

Hexadecimal numbers are those having a radix or base 16. There are 16 digits from 0 through F(15). A hexadecimal digit is used to denote a particular four-bit pattern in the zone or digit portion of a byte representing either a decimal number or an alphabetic or symbolic character. Hexadecimal digits and their decimal equivalents up to 65,535 are given in Table 1-2 along with an example of how to derive the decimal equivalent to a hexadecimal number.

| HEX  | DEC   | HEX | DEC   | HEX | DEC | HEX | DEC |

|------|-------|-----|-------|-----|-----|-----|-----|

| 0    | 0     | 0   | 0     | 0   | 0   | 0   | 0   |

| 1000 | 4096  | 100 | 256   | 10  | 16  | 1   | 1   |

| 2000 | 8192  | 200 | 512   | 20  | 32  | 2   | 2   |

| 3000 | 12288 | 300 | 768   | 30  | 48  | 3   | 3   |

| 4000 | 16384 | 400 | 1,024 | 40  | 64  | 4   | 4   |

| 5000 | 20480 | 500 | 1,280 | 50  | 80  | 5   | 5   |

| 6000 | 24576 | 600 | 1,536 | 60  | 96  | 6   | 6   |

| 7000 | 28672 | 700 | 1,792 | 70  | 112 | 7   | 7   |

| 8000 | 32768 | 800 | 2,048 | 80  | 128 | 8   | 8   |

| 9000 | 36864 | 900 | 2,304 | 90  | 144 | 9   | 9   |

| A000 | 40960 | A00 | 2,560 | A0  | 160 | Α   | 10  |

| B000 | 45056 | B00 | 2,816 | B0  | 176 | В   | 11  |

| C000 | 49152 | C00 | 3,072 | C0  | 192 | С   | 12  |

| D000 | 53248 | D00 | 3,328 | D0  | 208 | D   | 13  |

| E000 | 57344 | E00 | 3,584 | E0  | 224 | Ε   | 14  |

| F000 | 61440 | F00 | 3,840 | F0  | 240 | F   | 15  |

#### **EXAMPLE:**

Hexadecimal 39DB to Decimal

3000 = 12,288 900 = 2,304 D0 = 208 B = 11 39DB = 14,811

Table 1-2. Hexadecimal - Decimal Conversion

The expansion of Table 1-2, and tables for the powers of 2 and 16, are given in Appendix A.

#### 1.4.3. Decimal Number Representation

Decimal numbers are represented either in unpacked form (one digit per byte) or in packed form (two digits per byte). In unpacked form, the byte is divided into zone and digit positions.

The zone portion usually contains a hexadecimal F (1111), which is ignored except in the least significant byte; the zone portion of the least significant byte is interpreted as the sign of the number. In packed form, digits are contained in both halves of a byte, except the least significant half byte of the field, which is interpreted as the sign of the decimal number.

The sign of the decimal number is represented by hexadecimal digits A through F. Any other bit configuration is an invalid sign code, which could produce unpredictable results.

## 1.4.3.1. Sign Bits

The binary values of the sign bits are interpreted as follows:

0000 through 1000 positive number

1001 negative number

1010 positive number - generated by instructions in ASCII mode

1011 negative number - generated by instructions in ASCII mode

1100 positive number - generated by instructions in EBCDIC mode

1101 negative number - generated by instructions in EBCDIC mode

1110 positive number

1111 positive number

## 1.4.4. Character Representation

An alphabetic symbolic character uses eight bits of a byte and has no sign.

## 1.4.5. Parity Verification

The UNIVAC 9200/9200 II/9300/9300 II Systems processor uses odd parity for error checking. All data read from storage is given a parity check.

## 1.4.6. OP Codes

The OP code designations are expressed by two hexadecimal digits, in the 8-bit code shown, as follows: